探秘芬蘭金花大理石 天然石材的魅力與市場行情

在建筑裝飾領域,天然石材以其獨特的紋理、堅固的質地和自然的奢華感,始終占據著高端市場的一席之地。其中,大理石作為裝飾材料的經典選擇,其品種繁多,各具特色。建筑建材行業對一款名為“芬蘭金花”的大理石品種關注度頗高,尤其在以“世界工廠網”為代表的產品信息平臺上,出現了眾多廠家以“超低價供應”為賣點的信息。這背后是怎樣的市場邏輯?作為消費者或采購方,又應如何理性看待?本文將為您深入解析。

一、 認識“芬蘭金花”大理石

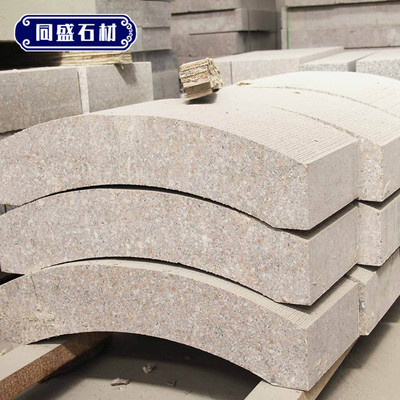

“芬蘭金花”并非產自芬蘭,而是一種以米黃色或淺金色為基調,伴有白色或不規則淺灰色花紋的大理石品種。其色澤溫潤、紋理靈動,既有皇家金的華貴,又不失清新淡雅,非常適合用于營造溫馨、大氣且不失格調的室內空間,常見于背景墻、地面鋪貼、窗臺、樓梯等部位的裝飾。

二、 天然石材價格的構成因素

天然石材的價格受多重因素影響,理解這些是判斷“超低價”是否合理的關鍵:

- 礦石品質與等級:同一品種的石材,根據板面的顏色均勻度、紋理美觀度、瑕疵(如裂紋、色斑、孔洞)的多少,會分為A級、B級、C級等不同等級,價差顯著。

- 開采與加工成本:包括礦山開采的難易度、荒料(大塊原石)的成材率、運輸費用,以及后期的切割、打磨、拋光、防護等加工工藝的精良程度。

- 市場供需與品牌:稀缺品種或流行款式價格自然走高。品牌廠家的產品在品控、服務和信譽上更有保障,價格也通常高于無名廠家。

- 規格與厚度:大板、工程板、規格板的價格模式不同,厚度增加也會提升成本和價格。

三、 “廠家超低價供應”現象剖析

在“世界工廠網”這類B2B信息平臺上,匯集了大量生產商和貿易商。出現“芬蘭金花超低價供應”的宣傳,可能源于以下幾種情況:

- 源頭廠家直銷:省略中間環節,直接從礦山或大型加工廠供貨,降低了流通成本。

- 庫存清理或尾貨處理:廠家為回籠資金,對部分等級稍低、或特定規格的庫存進行促銷。

- 市場競爭策略:尤其在行業淡季或新廠商為打開市場時,可能會以接近成本價或小幅利潤的價格吸引首批客戶。

- 需注意的“低價陷阱”:價格顯著低于市場平均水平時,需高度警惕。可能存在以次充好(用低等級冒充高等級)、偷工減料(厚度不足)、計算方式模糊(如按“平方米”報價但后續加收大量加工費)、或售后服務缺失等問題。

四、 給采購者的建議

- 明確需求,先看樣品:確定所需顏色、花紋、等級和規格。務必要求廠家寄送或實地查看大板樣品,確認實物與描述是否一致。

- 深究“低價”細節:詢問價格所包含的具體內容(是否含稅、運費、加工費、防護處理等),了解對應的石材等級和產地信息。

- 核查廠家資質:通過平臺信息、企業信用網站等渠道,核實廠家的生產規模、經營年限、客戶評價等,優先選擇信譽良好的供應商。

- 合同條款清晰化:在合同中明確產品等級、規格、數量、單價、總價、交貨時間、驗收標準、付款方式及質量違約責任,保護自身權益。

- 計算綜合成本:將材料費、加工費、損耗、運輸費、安裝費以及可能的維護成本一并考慮,評估整體項目的性價比。

###

“芬蘭金花”大理石作為優質的裝飾材料,其市場前景廣闊。面對“超低價供應”的信息,采購者應保持理性,秉持“一分錢一分貨”的市場基本原則,在追求合理成本的將產品質量、供應穩定性和售后服務放在同等重要的位置。通過細致的考察和規范的采購流程,才能最終實現以理想的價格,獲得真正物有所值的天然石材裝飾效果,為建筑空間增添持久的光彩與價值。

如若轉載,請注明出處:http://m.d0007.cn/product/63.html

更新時間:2026-04-17 02:34:55